窺口銅接線端子SC25-8 性能解析與市場供應概覽

窺口銅接線端子SC25-8是電氣連接領域中的一種常用組件,以其可靠的導電性能和便捷的安裝方式,廣泛應用于各類配電系統、機械設備及自動化控制電路中。本文將就其基本特性、市場價格因素、主要供應廠家及選購要點進行簡要介紹,并以金牛區景馳五金交電經營部為例,說明相關采購渠道。

一、產品特性與用途

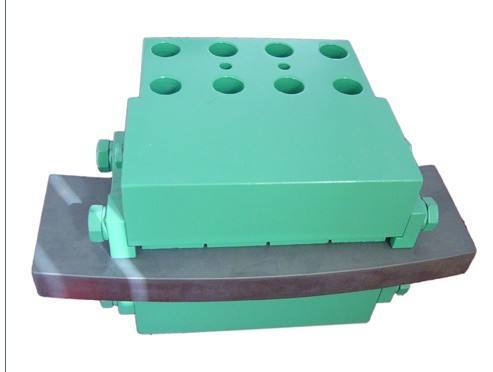

窺口銅接線端子SC25-8通常指窺口式(或稱為觀察口、透明窗口)設計的銅制接線端子,其型號中的“SC25-8”可能代表特定的規格尺寸(如適用導線截面、螺絲孔徑等)或系列代碼。窺口設計便于直接觀察內部導線壓接狀況,確保連接牢固安全,防止虛接或脫落。銅材質保證了優良的導電性和耐腐蝕性,適用于電流傳輸要求較高、環境較為復雜的場合。

二、價格與市場因素

該產品的價格受多重因素影響,主要包括原材料銅價的波動、生產工藝、品牌溢價、采購數量以及市場供需關系。一般來說,批量采購能獲得更優惠的單價。目前市場上,不同廠家和經銷商的報價可能存在差異,建議采購前多方詢價比較。金牛區景馳五金交電經營部作為專業的五金交電供應商,通常會提供具有競爭力的市場價格,具體需根據實時庫存和采購量進行咨詢。

三、廠家與供應商信息

生產窺口銅接線端子SC25-8的廠家眾多,遍布全國各大工業區,其中不乏知名電氣連接器品牌。這些廠家注重產品質量認證(如ISO標準、RoHS環保指令等),以確保端子符合安全規范。金牛區景馳五金交電經營部位于成都金牛區,是一家集銷售與服務于一體的五金交電經營實體,長期供應各類接線端子、連接器等產品,可為客戶提供SC25-8端子的現貨或訂貨服務,并附有詳細的產品圖片和規格參數供客戶確認。

四、選購與使用建議

在選購窺口銅接線端子SC25-8時,應注意以下幾點:確認端子規格與所用導線尺寸匹配,避免過松或過緊;檢查窺口是否清晰透明,便于后續維護檢查;優先選擇信譽良好的廠家或經銷商,如景馳五金交電經營部,以確保產品質量和售后服務;考慮產品是否具備必要的安全認證。使用時,應按照規范進行壓接,定期通過窺口檢查連接狀態,保障電氣系統穩定運行。

窺口銅接線端子SC25-8作為關鍵的連接器部件,其選擇關乎整個電路系統的安全與效率。通過了解產品特性、市場行情及可靠供應渠道,用戶能更高效地完成采購與應用。

如若轉載,請注明出處:http://www.niu1niu2niu.cn/product/48.html

更新時間:2026-04-14 19:53:38